Image: Wikimedia Commons.

| HI | LO-NIBBLE | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F | |

| 00 | BRK impl | ORA X,ind | --- | --- | --- | ORA zpg | ASL zpg | --- | PHP impl | ORA # | ASL A | --- | --- | ORA abs | ASL abs | --- |

| 10 | BPL rel | ORA ind,Y | --- | --- | --- | ORA zpg,X | ASL zpg,X | --- | CLC impl | ORA abs,Y | --- | --- | --- | ORA abs,X | ASL abs,X | --- |

| 20 | JSR abs | AND X,ind | --- | --- | BIT zpg | AND zpg | ROL zpg | --- | PLP impl | AND # | ROL A | --- | BIT abs | AND abs | ROL abs | --- |

| 30 | BMI rel | AND ind,Y | --- | --- | --- | AND zpg,X | ROL zpg,X | --- | SEC impl | AND abs,Y | --- | --- | --- | AND abs,X | ROL abs,X | --- |

| 40 | RTI impl | EOR X,ind | --- | --- | --- | EOR zpg | LSR zpg | --- | PHA impl | EOR # | LSR A | --- | JMP abs | EOR abs | LSR abs | --- |

| 50 | BVC rel | EOR ind,Y | --- | --- | --- | EOR zpg,X | LSR zpg,X | --- | CLI impl | EOR abs,Y | --- | --- | --- | EOR abs,X | LSR abs,X | --- |

| 60 | RTS impl | ADC X,ind | --- | --- | --- | ADC zpg | ROR zpg | --- | PLA impl | ADC # | ROR A | --- | JMP ind | ADC abs | ROR abs | --- |

| 70 | BVS rel | ADC ind,Y | --- | --- | --- | ADC zpg,X | ROR zpg,X | --- | SEI impl | ADC abs,Y | --- | --- | --- | ADC abs,X | ROR abs,X | --- |

| 80 | --- | STA X,ind | --- | --- | STY zpg | STA zpg | STX zpg | --- | DEY impl | --- | TXA impl | --- | STY abs | STA abs | STX abs | --- |

| 90 | BCC rel | STA ind,Y | --- | --- | STY zpg,X | STA zpg,X | STX zpg,Y | --- | TYA impl | STA abs,Y | TXS impl | --- | --- | STA abs,X | --- | --- |

| A0 | LDY # | LDA X,ind | LDX # | --- | LDY zpg | LDA zpg | LDX zpg | --- | TAY impl | LDA # | TAX impl | --- | LDY abs | LDA abs | LDX abs | --- |

| B0 | BCS rel | LDA ind,Y | --- | --- | LDY zpg,X | LDA zpg,X | LDX zpg,Y | --- | CLV impl | LDA abs,Y | TSX impl | --- | LDY abs,X | LDA abs,X | LDX abs,Y | --- |

| C0 | CPY # | CMP X,ind | --- | --- | CPY zpg | CMP zpg | DEC zpg | --- | INY impl | CMP # | DEX impl | --- | CPY abs | CMP abs | DEC abs | --- |

| D0 | BNE rel | CMP ind,Y | --- | --- | --- | CMP zpg,X | DEC zpg,X | --- | CLD impl | CMP abs,Y | --- | --- | --- | CMP abs,X | DEC abs,X | --- |

| E0 | CPX # | SBC X,ind | --- | --- | CPX zpg | SBC zpg | INC zpg | --- | INX impl | SBC # | NOP impl | --- | CPX abs | SBC abs | INC abs | --- |

| F0 | BEQ rel | SBC ind,Y | --- | --- | --- | SBC zpg,X | INC zpg,X | --- | SED impl | SBC abs,Y | --- | --- | --- | SBC abs,X | INC abs,X | --- |

Address Modes:

| A | Accumulator | OPC A | operand is AC (implied single byte instruction) | |

| abs | absolute | OPC $LLHH | operand is address $HHLL * | |

| abs,X | absolute, X-indexed | OPC $LLHH,X | operand is address; effective address is address incremented by X with carry ** | |

| abs,Y | absolute, Y-indexed | OPC $LLHH,Y | operand is address; effective address is address incremented by Y with carry ** | |

| # | immediate | OPC #$BB | operand is byte BB | |

| impl | implied | OPC | operand implied | |

| ind | indirect | OPC ($LLHH) | operand is address; effective address is contents of word at address: C.w($HHLL) | |

| X,ind | X-indexed, indirect | OPC ($LL,X) | operand is zeropage address; effective address is word in (LL + X, LL + X + 1), inc. without carry: C.w($00LL + X) | |

| ind,Y | indirect, Y-indexed | OPC ($LL),Y | operand is zeropage address; effective address is word in (LL, LL + 1) incremented by Y with carry: C.w($00LL) + Y | |

| rel | relative | OPC $BB | branch target is PC + signed offset BB *** | |

| zpg | zeropage | OPC $LL | operand is zeropage address (hi-byte is zero, address = $00LL) | |

| zpg,X | zeropage, X-indexed | OPC $LL,X | operand is zeropage address; effective address is address incremented by X without carry ** | |

| zpg,Y | zeropage, Y-indexed | OPC $LL,Y | operand is zeropage address; effective address is address incremented by Y without carry ** |

* 16-bit address words are little endian, lo(w)-byte first, followed by the hi(gh)-byte.

(An assembler will use a human readable, big-endian notation as in $HHLL.)

** The available 16-bit address space is conceived as consisting of pages of 256 bytes each, with

address hi-bytes represententing the page index. An increment with carry may affect the hi-byte

and may thus result in a crossing of page boundaries, adding an extra cycle to the execution.

Increments without carry do not affect the hi-byte of an address and no page transitions do occur.

Generally, increments of 16-bit addresses include a carry, increments of zeropage addresses don't.

Notably this is not related in any way to the state of the carry bit of the accumulator.

*** Branch offsets are signed 8-bit values, -128 ... +127, negative offsets in two's complement.

Page transitions may occur and add an extra cycle to the exucution.

Instructions by Name:

| ADC | add with carry |

| AND | and (with accumulator) |

| ASL | arithmetic shift left |

| BCC | branch on carry clear |

| BCS | branch on carry set |

| BEQ | branch on equal (zero set) |

| BIT | bit test |

| BMI | branch on minus (negative set) |

| BNE | branch on not equal (zero clear) |

| BPL | branch on plus (negative clear) |

| BRK | break / interrupt |

| BVC | branch on overflow clear |

| BVS | branch on overflow set |

| CLC | clear carry |

| CLD | clear decimal |

| CLI | clear interrupt disable |

| CLV | clear overflow |

| CMP | compare (with accumulator) |

| CPX | compare with X |

| CPY | compare with Y |

| DEC | decrement |

| DEX | decrement X |

| DEY | decrement Y |

| EOR | exclusive or (with accumulator) |

| INC | increment |

| INX | increment X |

| INY | increment Y |

| JMP | jump |

| JSR | jump subroutine |

| LDA | load accumulator |

| LDX | load X |

| LDY | load Y |

| LSR | logical shift right |

| NOP | no operation |

| ORA | or with accumulator |

| PHA | push accumulator |

| PHP | push processor status (SR) |

| PLA | pull accumulator |

| PLP | pull processor status (SR) |

| ROL | rotate left |

| ROR | rotate right |

| RTI | return from interrupt |

| RTS | return from subroutine |

| SBC | subtract with carry |

| SEC | set carry |

| SED | set decimal |

| SEI | set interrupt disable |

| STA | store accumulator |

| STX | store X |

| STY | store Y |

| TAX | transfer accumulator to X |

| TAY | transfer accumulator to Y |

| TSX | transfer stack pointer to X |

| TXA | transfer X to accumulator |

| TXS | transfer X to stack pointer |

| TYA | transfer Y to accumulator |

Registers:

| PC | program counter | (16 bit) | |

| AC | accumulator | (8 bit) | |

| X | X register | (8 bit) | |

| Y | Y register | (8 bit) | |

| SR | status register [NV-BDIZC] | (8 bit) | |

| SP | .... | stack pointer | (8 bit) |

SR Flags (bit 7 to bit 0):

| N | Negative |

| V | Overflow |

| - | ignored |

| B | Break |

| D | Decimal (use BCD for arithmetics) |

| I | Interrupt (IRQ disable) |

| Z | Zero |

| C | Carry |

Processor Stack:

LIFO, top down, 8 bit range, 0x0100 - 0x01FF

Bytes, Words, Addressing:

8 bit bytes, 16 bit words in lobyte-hibyte representation (Little-Endian).

16 bit address range, operands follow instruction codes.

Signed values are two's complement, sign in bit 7 (most significant bit).

(%11111111 = $FF = -1, %10000000 = $80 = -128, %01111111 = $7F = +127)

Vendor:

MOS Technology, 1975

Image: Wikimedia Commons.

ADC Add Memory to Accumulator with Carry A + M + C -> A, C N Z C I D V + + + - - + addressing assembler opc bytes cyles -------------------------------------------- immidiate ADC #oper 69 2 2 zeropage ADC oper 65 2 3 zeropage,X ADC oper,X 75 2 4 absolute ADC oper 6D 3 4 absolute,X ADC oper,X 7D 3 4* absolute,Y ADC oper,Y 79 3 4* (indirect,X) ADC (oper,X) 61 2 6 (indirect),Y ADC (oper),Y 71 2 5* AND AND Memory with Accumulator A AND M -> A N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- immidiate AND #oper 29 2 2 zeropage AND oper 25 2 3 zeropage,X AND oper,X 35 2 4 absolute AND oper 2D 3 4 absolute,X AND oper,X 3D 3 4* absolute,Y AND oper,Y 39 3 4* (indirect,X) AND (oper,X) 21 2 6 (indirect),Y AND (oper),Y 31 2 5* ASL Shift Left One Bit (Memory or Accumulator) C <- [76543210] <- 0 N Z C I D V + + + - - - addressing assembler opc bytes cyles -------------------------------------------- accumulator ASL A 0A 1 2 zeropage ASL oper 06 2 5 zeropage,X ASL oper,X 16 2 6 absolute ASL oper 0E 3 6 absolute,X ASL oper,X 1E 3 7 BCC Branch on Carry Clear branch on C = 0 N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- relative BCC oper 90 2 2** BCS Branch on Carry Set branch on C = 1 N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- relative BCS oper B0 2 2** BEQ Branch on Result Zero branch on Z = 1 N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- relative BEQ oper F0 2 2** BIT Test Bits in Memory with Accumulator bits 7 and 6 of operand are transfered to bit 7 and 6 of SR (N,V); the zeroflag is set to the result of operand AND accumulator. A AND M, M7 -> N, M6 -> V N Z C I D V M7 + - - - M6 addressing assembler opc bytes cyles -------------------------------------------- zeropage BIT oper 24 2 3 absolute BIT oper 2C 3 4 BMI Branch on Result Minus branch on N = 1 N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- relative BMI oper 30 2 2** BNE Branch on Result not Zero branch on Z = 0 N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- relative BNE oper D0 2 2** BPL Branch on Result Plus branch on N = 0 N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- relative BPL oper 10 2 2** BRK Force Break interrupt, N Z C I D V push PC+2, push SR - - - 1 - - addressing assembler opc bytes cyles -------------------------------------------- implied BRK 00 1 7 BVC Branch on Overflow Clear branch on V = 0 N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- relative BVC oper 50 2 2** BVS Branch on Overflow Set branch on V = 1 N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- relative BVC oper 70 2 2** CLC Clear Carry Flag 0 -> C N Z C I D V - - 0 - - - addressing assembler opc bytes cyles -------------------------------------------- implied CLC 18 1 2 CLD Clear Decimal Mode 0 -> D N Z C I D V - - - - 0 - addressing assembler opc bytes cyles -------------------------------------------- implied CLD D8 1 2 CLI Clear Interrupt Disable Bit 0 -> I N Z C I D V - - - 0 - - addressing assembler opc bytes cyles -------------------------------------------- implied CLI 58 1 2 CLV Clear Overflow Flag 0 -> V N Z C I D V - - - - - 0 addressing assembler opc bytes cyles -------------------------------------------- implied CLV B8 1 2 CMP Compare Memory with Accumulator A - M N Z C I D V + + + - - - addressing assembler opc bytes cyles -------------------------------------------- immidiate CMP #oper C9 2 2 zeropage CMP oper C5 2 3 zeropage,X CMP oper,X D5 2 4 absolute CMP oper CD 3 4 absolute,X CMP oper,X DD 3 4* absolute,Y CMP oper,Y D9 3 4* (indirect,X) CMP (oper,X) C1 2 6 (indirect),Y CMP (oper),Y D1 2 5* CPX Compare Memory and Index X X - M N Z C I D V + + + - - - addressing assembler opc bytes cyles -------------------------------------------- immidiate CPX #oper E0 2 2 zeropage CPX oper E4 2 3 absolute CPX oper EC 3 4 CPY Compare Memory and Index Y Y - M N Z C I D V + + + - - - addressing assembler opc bytes cyles -------------------------------------------- immidiate CPY #oper C0 2 2 zeropage CPY oper C4 2 3 absolute CPY oper CC 3 4 DEC Decrement Memory by One M - 1 -> M N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- zeropage DEC oper C6 2 5 zeropage,X DEC oper,X D6 2 6 absolute DEC oper CE 3 6 absolute,X DEC oper,X DE 3 7 DEX Decrement Index X by One X - 1 -> X N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- implied DEC CA 1 2 DEY Decrement Index Y by One Y - 1 -> Y N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- implied DEC 88 1 2 EOR Exclusive-OR Memory with Accumulator A EOR M -> A N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- immidiate EOR #oper 49 2 2 zeropage EOR oper 45 2 3 zeropage,X EOR oper,X 55 2 4 absolute EOR oper 4D 3 4 absolute,X EOR oper,X 5D 3 4* absolute,Y EOR oper,Y 59 3 4* (indirect,X) EOR (oper,X) 41 2 6 (indirect),Y EOR (oper),Y 51 2 5* INC Increment Memory by One M + 1 -> M N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- zeropage INC oper E6 2 5 zeropage,X INC oper,X F6 2 6 absolute INC oper EE 3 6 absolute,X INC oper,X FE 3 7 INX Increment Index X by One X + 1 -> X N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- implied INX E8 1 2 INY Increment Index Y by One Y + 1 -> Y N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- implied INY C8 1 2 JMP Jump to New Location (PC+1) -> PCL N Z C I D V (PC+2) -> PCH - - - - - - addressing assembler opc bytes cyles -------------------------------------------- absolute JMP oper 4C 3 3 indirect JMP (oper) 6C 3 5 JSR Jump to New Location Saving Return Address push (PC+2), N Z C I D V (PC+1) -> PCL - - - - - - (PC+2) -> PCH addressing assembler opc bytes cyles -------------------------------------------- absolute JSR oper 20 3 6 LDA Load Accumulator with Memory M -> A N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- immidiate LDA #oper A9 2 2 zeropage LDA oper A5 2 3 zeropage,X LDA oper,X B5 2 4 absolute LDA oper AD 3 4 absolute,X LDA oper,X BD 3 4* absolute,Y LDA oper,Y B9 3 4* (indirect,X) LDA (oper,X) A1 2 6 (indirect),Y LDA (oper),Y B1 2 5* LDX Load Index X with Memory M -> X N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- immidiate LDX #oper A2 2 2 zeropage LDX oper A6 2 3 zeropage,Y LDX oper,Y B6 2 4 absolute LDX oper AE 3 4 absolute,Y LDX oper,Y BE 3 4* LDY Load Index Y with Memory M -> Y N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- immidiate LDY #oper A0 2 2 zeropage LDY oper A4 2 3 zeropage,X LDY oper,X B4 2 4 absolute LDY oper AC 3 4 absolute,X LDY oper,X BC 3 4* LSR Shift One Bit Right (Memory or Accumulator) 0 -> [76543210] -> C N Z C I D V 0 + + - - - addressing assembler opc bytes cyles -------------------------------------------- accumulator LSR A 4A 1 2 zeropage LSR oper 46 2 5 zeropage,X LSR oper,X 56 2 6 absolute LSR oper 4E 3 6 absolute,X LSR oper,X 5E 3 7 NOP No Operation --- N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- implied NOP EA 1 2 ORA OR Memory with Accumulator A OR M -> A N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- immidiate ORA #oper 09 2 2 zeropage ORA oper 05 2 3 zeropage,X ORA oper,X 15 2 4 absolute ORA oper 0D 3 4 absolute,X ORA oper,X 1D 3 4* absolute,Y ORA oper,Y 19 3 4* (indirect,X) ORA (oper,X) 01 2 6 (indirect),Y ORA (oper),Y 11 2 5* PHA Push Accumulator on Stack push A N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- implied PHA 48 1 3 PHP Push Processor Status on Stack push SR N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- implied PHP 08 1 3 PLA Pull Accumulator from Stack pull A N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- implied PLA 68 1 4 PLP Pull Processor Status from Stack pull SR N Z C I D V from stack addressing assembler opc bytes cyles -------------------------------------------- implied PLP 28 1 4 ROL Rotate One Bit Left (Memory or Accumulator) C <- [76543210] <- C N Z C I D V + + + - - - addressing assembler opc bytes cyles -------------------------------------------- accumulator ROL A 2A 1 2 zeropage ROL oper 26 2 5 zeropage,X ROL oper,X 36 2 6 absolute ROL oper 2E 3 6 absolute,X ROL oper,X 3E 3 7 ROR Rotate One Bit Right (Memory or Accumulator) C -> [76543210] -> C N Z C I D V + + + - - - addressing assembler opc bytes cyles -------------------------------------------- accumulator ROR A 6A 1 2 zeropage ROR oper 66 2 5 zeropage,X ROR oper,X 76 2 6 absolute ROR oper 6E 3 6 absolute,X ROR oper,X 7E 3 7 RTI Return from Interrupt pull SR, pull PC N Z C I D V from stack addressing assembler opc bytes cyles -------------------------------------------- implied RTI 40 1 6 RTS Return from Subroutine pull PC, PC+1 -> PC N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- implied RTS 60 1 6 SBC Subtract Memory from Accumulator with Borrow A - M - -> A N Z C I D V + + + - - + addressing assembler opc bytes cyles -------------------------------------------- immidiate SBC #oper E9 2 2 zeropage SBC oper E5 2 3 zeropage,X SBC oper,X F5 2 4 absolute SBC oper ED 3 4 absolute,X SBC oper,X FD 3 4* absolute,Y SBC oper,Y F9 3 4* (indirect,X) SBC (oper,X) E1 2 6 (indirect),Y SBC (oper),Y F1 2 5* SEC Set Carry Flag 1 -> C N Z C I D V - - 1 - - - addressing assembler opc bytes cyles -------------------------------------------- implied SEC 38 1 2 SED Set Decimal Flag 1 -> D N Z C I D V - - - - 1 - addressing assembler opc bytes cyles -------------------------------------------- implied SED F8 1 2 SEI Set Interrupt Disable Status 1 -> I N Z C I D V - - - 1 - - addressing assembler opc bytes cyles -------------------------------------------- implied SEI 78 1 2 STA Store Accumulator in Memory A -> M N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- zeropage STA oper 85 2 3 zeropage,X STA oper,X 95 2 4 absolute STA oper 8D 3 4 absolute,X STA oper,X 9D 3 5 absolute,Y STA oper,Y 99 3 5 (indirect,X) STA (oper,X) 81 2 6 (indirect),Y STA (oper),Y 91 2 6 STX Store Index X in Memory X -> M N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- zeropage STX oper 86 2 3 zeropage,Y STX oper,Y 96 2 4 absolute STX oper 8E 3 4 STY Sore Index Y in Memory Y -> M N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- zeropage STY oper 84 2 3 zeropage,X STY oper,X 94 2 4 absolute STY oper 8C 3 4 TAX Transfer Accumulator to Index X A -> X N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- implied TAX AA 1 2 TAY Transfer Accumulator to Index Y A -> Y N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- implied TAY A8 1 2 TSX Transfer Stack Pointer to Index X SP -> X N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- implied TSX BA 1 2 TXA Transfer Index X to Accumulator X -> A N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- implied TXA 8A 1 2 TXS Transfer Index X to Stack Register X -> SP N Z C I D V - - - - - - addressing assembler opc bytes cyles -------------------------------------------- implied TXS 9A 1 2 TYA Transfer Index Y to Accumulator Y -> A N Z C I D V + + - - - - addressing assembler opc bytes cyles -------------------------------------------- implied TYA 98 1 2 * add 1 to cycles if page boundery is crossed ** add 1 to cycles if branch occurs on same page add 2 to cycles if branch occurs to different page Legend to Flags: + .... modified - .... not modified 1 .... set 0 .... cleared M6 .... memory bit 6 M7 .... memory bit 7 Note on assembler syntax: Most assemblers employ "OPC *oper" for forced zeropage addressing.

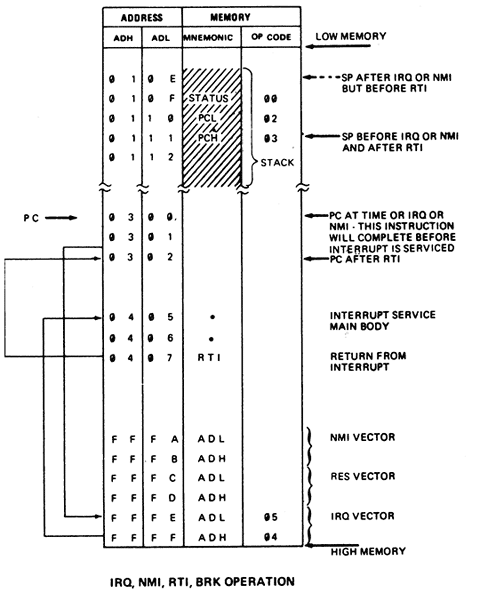

The 256 bytes processor stack of the 6502 is located at $0100 ... $01FF in

memory, growing down from top to bottom.

There are three 2-byte address locations at the very top end of the 64K address

space serving as jump vectors for reset/startup and interrupt operations:

$FFFA, $FFFB ... NMI (Non-Maskable Interrupt) vector

$FFFC, $FFFD ... RES (Reset) vector

$FFFE, $FFFF ... IRQ (Interrupt Request) vector

At the occurrence of interrupt, the value of the program counter (PC) is put in

high-low order onto the stack, followed by the value currently in the status

register and control will be transferred to the address location found in the

respective interrupt vector. These are recovered from the stack at the end of

an interrupt routine by the RTI instruction.

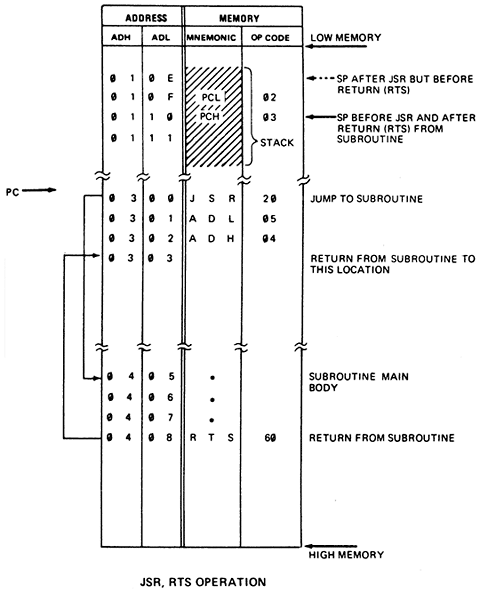

Similarly, as a JSR instruction is encountered, PC is dumped onto the stack

and recovered by the JSR instruction:

The 6502 instruction table is laid out according to a pattern a-b-c, where

a and b are an octal number each, followed by a group of two binary digits c,

as in the bit-vector "aaabbbcc".

| a | a | a | b | b | b | c | c | |

| bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| (0…7) | (0…7) | (0…3) | ||||||

Example:

All ROR instructions share a = 3 and c = 2 (3b2) with the address mode in b.

At the same time, all instructions addressing the zero-page share b = 1 (a1c).

abc = 312 => ( 3 << 5 | 1 << 2 | 2 ) = %011.001.10 = $66 "ROR zpg".

Notably, there are no legal opcodes defined where c = 3, accounting for the

empty columns in the usual, hexadecimal view of the instruction table.

(For compactness empty rows where c = 3 are omitted from the tables below.)

The following table lists the instruction set, rows sorted by c, then a.

Generally, instructions of a kind are typically found in rows as a combination

of a and c, and address modes are in columns b.

However, there are a few exception to this rule, namely, where bits 0 of both

c and b are low (c = 0, 2; b = 0, 2, 4, 6) and combinations of c and b select

a group of related operations. (E.g., c=0 ∧ b=4: branch, c=0 ∧ b=6: set flag)

| c | a | b | |||||||

|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | ||

| 0 | 0 | $00BRK impl | $08PHP impl | $10BPL rel | $18CLC impl | ||||

| 1 | $20JSR abs | $24BIT zpg | $28PLP impl | $2CBIT abs | $30BMI rel | $38SEC impl | |||

| 2 | $40RTI impl | $48PHA impl | $4CJMP abs | $50BVC rel | $58CLI impl | ||||

| 3 | $60RTS impl | $68PLA impl | $6CJMP ind | $70BVS rel | $78SEI impl | ||||

| 4 | $84STY zpg | $88DEY impl | $8CSTY abs | $90BCC rel | $94STY zpg,X | $98TYA impl | |||

| 5 | $A0LDY # | $A4LDY zpg | $A8TAY impl | $ACLDY abs | $B0BCS rel | $B4LDY zpg,X | $B8CLV impl | $BCLDY abs,X | |

| 6 | $C0CPY # | $C4CPY zpg | $C8INY impl | $CCCPY abs | $D0BNE rel | $D8CLD impl | |||

| 7 | $E0CPX # | $E4CPX zpg | $E8INX impl | $ECCPX abs | $F0BEQ rel | $F8SED impl | |||

| 1 | 0 | $01ORA X,ind | $05ORA zpg | $09ORA # | $0DORA abs | $11ORA ind,Y | $15ORA zpg,X | $19ORA abs,Y | $1DORA abs,X |

| 1 | $21AND X,ind | $25AND zpg | $29AND # | $2DAND abs | $31AND ind,Y | $35AND zpg,X | $39AND abs,Y | $3DAND abs,X | |

| 2 | $41EOR X,ind | $45EOR zpg | $49EOR # | $4DEOR abs | $51EOR ind,Y | $55EOR zpg,X | $59EOR abs,Y | $5DEOR abs,X | |

| 3 | $61ADC X,ind | $65ADC zpg | $69ADC # | $6DADC abs | $71ADC ind,Y | $75ADC zpg,X | $79ADC abs,Y | $7DADC abs,X | |

| 4 | $81STA X,ind | $85STA zpg | $8DSTA abs | $91STA ind,Y | $95STA zpg,X | $99STA abs,Y | $9DSTA abs,X | ||

| 5 | $A1LDA X,ind | $A5LDA zpg | $A9LDA # | $ADLDA abs | $B1LDA ind,Y | $B5LDA zpg,X | $B9LDA abs,Y | $BDLDA abs,X | |

| 6 | $C1CMP X,ind | $C5CMP zpg | $C9CMP # | $CDCMP abs | $D1CMP ind,Y | $D5CMP zpg,X | $D9CMP abs,Y | $DDCMP abs,X | |

| 7 | $E1SBC X,ind | $E5SBC zpg | $E9SBC # | $EDSBC abs | $F1SBC ind,Y | $F5SBC zpg,X | $F9SBC abs,Y | $FDSBC abs,X | |

| 2 | 0 | $06ASL zpg | $0AASL A | $0EASL abs | $16ASL zpg,X | $1EASL abs,X | |||

| 1 | $26ROL zpg | $2AROL A | $2EROL abs | $36ROL zpg,X | $3EROL abs,X | ||||

| 2 | $46LSR zpg | $4ALSR A | $4ELSR abs | $56LSR zpg,X | $5ELSR abs,X | ||||

| 3 | $66ROR zpg | $6AROR A | $6EROR abs | $76ROR zpg,X | $7EROR abs,X | ||||

| 4 | $86STX zpg | $8ATXA impl | $8ESTX abs | $96STX zpg,Y | $9ATXS impl | ||||

| 5 | $A2LDX # | $A6LDX zpg | $AATAX impl | $AELDX abs | $B6LDX zpg,Y | $BATSX impl | $BELDX abs,Y | ||

| 6 | $C6DEC zpg | $CADEX impl | $CEDEC abs | $D6DEC zpg,X | $DEDEC abs,X | ||||

| 7 | $E6INC zpg | $EANOP impl | $EEINC abs | $F6INC zpg,X | $FEINC abs,X | ||||

Note: The operand of instructions like "ASL A" is essentially implied, as well.

However, for consistency, they are here listed in the usual "CMD A" notation,

instead of "CMD impl". Mind that the two notations are interchangeable for any

instructions involving the accumulator.

A rotated view, rows as combinations of c and b, and columns as a:

| c | b | a | |||||||

|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | ||

| 0 | 0 | $00BRK impl | $20JSR abs | $40RTI impl | $60RTS impl | $A0LDY # | $C0CPY # | $E0CPX # | |

| 1 | $24BIT zpg | $84STY zpg | $A4LDY zpg | $C4CPY zpg | $E4CPX zpg | ||||

| 2 | $08PHP impl | $28PLP impl | $48PHA impl | $68PLA impl | $88DEY impl | $A8TAY impl | $C8INY impl | $E8INX impl | |

| 3 | $2CBIT abs | $4CJMP abs | $6CJMP ind | $8CSTY abs | $ACLDY abs | $CCCPY abs | $ECCPX abs | ||

| 4 | $10BPL rel | $30BMI rel | $50BVC rel | $70BVS rel | $90BCC rel | $B0BCS rel | $D0BNE rel | $F0BEQ rel | |

| 5 | $94STY zpg,X | $B4LDY zpg,X | |||||||

| 6 | $18CLC impl | $38SEC impl | $58CLI impl | $78SEI impl | $98TYA impl | $B8CLV impl | $D8CLD impl | $F8SED impl | |

| 7 | $BCLDY abs,X | ||||||||

| 1 | 0 | $01ORA X,ind | $21AND X,ind | $41EOR X,ind | $61ADC X,ind | $81STA X,ind | $A1LDA X,ind | $C1CMP X,ind | $E1SBC X,ind |

| 1 | $05ORA zpg | $25AND zpg | $45EOR zpg | $65ADC zpg | $85STA zpg | $A5LDA zpg | $C5CMP zpg | $E5SBC zpg | |

| 2 | $09ORA # | $29AND # | $49EOR # | $69ADC # | $A9LDA # | $C9CMP # | $E9SBC # | ||

| 3 | $0DORA abs | $2DAND abs | $4DEOR abs | $6DADC abs | $8DSTA abs | $ADLDA abs | $CDCMP abs | $EDSBC abs | |

| 4 | $11ORA ind,Y | $31AND ind,Y | $51EOR ind,Y | $71ADC ind,Y | $91STA ind,Y | $B1LDA ind,Y | $D1CMP ind,Y | $F1SBC ind,Y | |

| 5 | $15ORA zpg,X | $35AND zpg,X | $55EOR zpg,X | $75ADC zpg,X | $95STA zpg,X | $B5LDA zpg,X | $D5CMP zpg,X | $F5SBC zpg,X | |

| 6 | $19ORA abs,Y | $39AND abs,Y | $59EOR abs,Y | $79ADC abs,Y | $99STA abs,Y | $B9LDA abs,Y | $D9CMP abs,Y | $F9SBC abs,Y | |

| 7 | $1DORA abs,X | $3DAND abs,X | $5DEOR abs,X | $7DADC abs,X | $9DSTA abs,X | $BDLDA abs,X | $DDCMP abs,X | $FDSBC abs,X | |

| 2 | 0 | $A2LDX # | |||||||

| 1 | $06ASL zpg | $26ROL zpg | $46LSR zpg | $66ROR zpg | $86STX zpg | $A6LDX zpg | $C6DEC zpg | $E6INC zpg | |

| 2 | $0AASL A | $2AROL A | $4ALSR A | $6AROR A | $8ATXA impl | $AATAX impl | $CADEX impl | $EANOP impl | |

| 3 | $0EASL abs | $2EROL abs | $4ELSR abs | $6EROR abs | $8ESTX abs | $AELDX abs | $CEDEC abs | $EEINC abs | |

| 4 | |||||||||

| 5 | $16ASL zpg,X | $36ROL zpg,X | $56LSR zpg,X | $76ROR zpg,X | $96STX zpg,Y | $B6LDX zpg,Y | $D6DEC zpg,X | $F6INC zpg,X | |

| 6 | $9ATXS impl | $BATSX impl | |||||||

| 7 | $1EASL abs,X | $3EROL abs,X | $5ELSR abs,X | $7EROR abs,X | $BELDX abs,Y | $DEDEC abs,X | $FEINC abs,X | ||

Finally, a more complex view, the instruction set listed by rows as

combinations of a and c, and b in columns:

Address modes are either a property of b (even columns) or combinations

of b and c (odd columns with aspecific row-index modulus 3; i.e., every

third row in a given column). In those latter columns, first and third

rows (c = 0 and c = 2) refer to the same kind of general operation.

Load, store and transfer instructions as well as comparisons are typically

found in the lower half of the table, while most of the arithmetical and

logical operations as well as stack and jump instructions are found in the

upper half. (However, mind the exception of SBC as a "mirror" of ADC.)

| a | c | b | |||||||

|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | ||

| 0 | 0 | $00BRK impl | $08PHP impl | $10BPL rel | $18CLC impl | ||||

| 1 | $01ORA X,ind | $05ORA zpg | $09ORA # | $0DORA abs | $11ORA ind,Y | $15ORA zpg,X | $19ORA abs,Y | $1DORA abs,X | |

| 2 | $06ASL zpg | $0AASL A | $0EASL abs | $16ASL zpg,X | $1EASL abs,X | ||||

| 1 | 0 | $20JSR abs | $24BIT zpg | $28PLP impl | $2CBIT abs | $30BMI rel | $38SEC impl | ||

| 1 | $21AND X,ind | $25AND zpg | $29AND # | $2DAND abs | $31AND ind,Y | $35AND zpg,X | $39AND abs,Y | $3DAND abs,X | |

| 2 | $26ROL zpg | $2AROL A | $2EROL abs | $36ROL zpg,X | $3EROL abs,X | ||||

| 2 | 0 | $40RTI impl | $48PHA impl | $4CJMP abs | $50BVC rel | $58CLI impl | |||

| 1 | $41EOR X,ind | $45EOR zpg | $49EOR # | $4DEOR abs | $51EOR ind,Y | $55EOR zpg,X | $59EOR abs,Y | $5DEOR abs,X | |

| 2 | $46LSR zpg | $4ALSR A | $4ELSR abs | $56LSR zpg,X | $5ELSR abs,X | ||||

| 3 | 0 | $60RTS impl | $68PLA impl | $6CJMP ind | $70BVS rel | $78SEI impl | |||

| 1 | $61ADC X,ind | $65ADC zpg | $69ADC # | $6DADC abs | $71ADC ind,Y | $75ADC zpg,X | $79ADC abs,Y | $7DADC abs,X | |

| 2 | $66ROR zpg | $6AROR A | $6EROR abs | $76ROR zpg,X | $7EROR abs,X | ||||

| 4 | 0 | $84STY zpg | $88DEY impl | $8CSTY abs | $90BCC rel | $94STY zpg,X | $98TYA impl | ||

| 1 | $81STA X,ind | $85STA zpg | $8DSTA abs | $91STA ind,Y | $95STA zpg,X | $99STA abs,Y | $9DSTA abs,X | ||

| 2 | $86STX zpg | $8ATXA impl | $8ESTX abs | $96STX zpg,Y | $9ATXS impl | ||||

| 5 | 0 | $A0LDY # | $A4LDY zpg | $A8TAY impl | $ACLDY abs | $B0BCS rel | $B4LDY zpg,X | $B8CLV impl | $BCLDY abs,X |

| 1 | $A1LDA X,ind | $A5LDA zpg | $A9LDA # | $ADLDA abs | $B1LDA ind,Y | $B5LDA zpg,X | $B9LDA abs,Y | $BDLDA abs,X | |

| 2 | $A2LDX # | $A6LDX zpg | $AATAX impl | $AELDX abs | $B6LDX zpg,Y | $BATSX impl | $BELDX abs,Y | ||

| 6 | 0 | $C0CPY # | $C4CPY zpg | $C8INY impl | $CCCPY abs | $D0BNE rel | $D8CLD impl | ||

| 1 | $C1CMP X,ind | $C5CMP zpg | $C9CMP # | $CDCMP abs | $D1CMP ind,Y | $D5CMP zpg,X | $D9CMP abs,Y | $DDCMP abs,X | |

| 2 | $C6DEC zpg | $CADEX impl | $CEDEC abs | $D6DEC zpg,X | $DEDEC abs,X | ||||

| 7 | 0 | $E0CPX # | $E4CPX zpg | $E8INX impl | $ECCPX abs | $F0BEQ rel | $F8SED impl | ||

| 1 | $E1SBC X,ind | $E5SBC zpg | $E9SBC # | $EDSBC abs | $F1SBC ind,Y | $F5SBC zpg,X | $F9SBC abs,Y | $FDSBC abs,X | |

| 2 | $E6INC zpg | $EANOP impl | $EEINC abs | $F6INC zpg,X | $FEINC abs,X | ||||

Type Features, Comments ------------------------------------- 6502 NMOS, 16 bit address bus, 8 bit data bus 6502A accelerated version of 6502 6502C accelerated version of 6502, additional halt pin, CMOS 65C02 16 bit version, additional instructions and address modes 6503, 6505, 6506 12 bit address bus [4 KiB] 6504 13 bit address bus [8 KiB] 6507 13 bit address bus [8 KiB], no interrupts 6509 20 bit address bus [1 MiB] by bankswitching 6510 as 6502 with additional 6 bit I/O-port 6511 integrated micro controler with I/O-port, serial interface, and RAM (Rockwell) 65F11 as 6511, integrated FORTH interpreter 7501 as 6502, HMOS 8500 as 6510, CMOS 8502 as 6510 with switchable 2 MHz option, 7 bit I/O-port 65816 (65C816) 16 bit registers and ALU, 24 bit address bus [16 MiB], up to 24 MHz (Western Design Center) 65802 (65C802) as 65816, pin compatible to 6502, 64 KiB address bus, up to 16 MHz

Disclaimer:

Errors excepted. The information is provided for free and AS IS, therefore without any warranty;

without even the implied warranty of merchantability or fitness for a particular purpose.

See also:

>> Virtual 6502 (6502/6510 emulator)

>> 6502 Assembler

>> 6502 Disassembler

External Links:

>> 6502.org — the 6502 microprocessor resource

>> visual6502.org — visual transistor-level simulation of the 6502 CPU

>> The Western Design Center, Inc. — designers of the 6502 (still thriving)

Presented by virtual 6502, mass:werk.